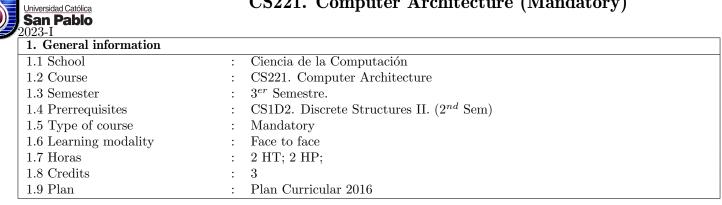

# San Pablo Catholic University (UCSP) **Undergraduate Program in Computer Science** SILABO

# CS221. Computer Architecture (Mandatory)

### 2. Professors

# Lecturer

• Yván Jesús Túpac Valdivia <vtupac@ucsp.edu.pe> - PhD in Ingeniería Eléctrica, Pontificia Universidad Católica de Rio de Janeiro, Brasil, 2005.

### **3.** Course foundation

A computer scientist must have a solid knowledge of the organization and design principles of diverse computer systems, by understanding the limitations of modern systems they could propose next-gen paradigms. This course teaches the basics and principles of Computer Architecture. This class address digital logic design, basics of Computer Architecture and processor design (Instruction Set architecture, microarchitecture, out-of-order execution, branch prediction), execution paradigms (superscalar, dataflow, VLIW, SIMD, GPUs, systolic, multithreading) and memory system organization.

#### 4. Summary

1. Digital logic and digital systems 2. Machine level representation of data 3. Assembly level machine organization 4. Functional organization 5. Memory system organization and architecture 6. Interfacing and communication 7. Multiprocessing and alternative architectures 8. Performance enhancements

#### 5. Generales Goals

- Provide a first approach in Computer Architecture.

- Study the design and evolution of computer architectures, which lead to modern approaches and implementations in computing systems.

- Provide fine-grained details of computer hardware, and its relation with software execution.

- Implement a simple microprocessor using Verilog language.

#### 6. Contribution to Outcomes

This discipline contributes to the achievement of the following outcomes:

- 1) Analyze a complex computing problem and to apply principles of computing and other relevant disciplines to identify solutions. (Usage)

- 6) Apply computer science theory and software development fundamentals to produce computing-based solutions. (Assessment)

## 7. Content

| Competences:                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Content                                                                                                                                                                                                                                                                                                                       | Generales Goals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| <ul> <li>Bits, bytes, and words</li> <li>Numeric data representation and number bases</li> <li>Fixed- and floating-point systems</li> <li>Signed and twos-complement representations</li> <li>Representation of non-numeric data (character codes, graphical data)</li> <li>Representation of registers and arrays</li> </ul> | <ul> <li>Explain why everything is data, including instructions, in computers [Assessment]</li> <li>Explain the reasons for using alternative formats the represent numerical data [Familiarity]</li> <li>Describe how negative integers are stored in sign magnitude and twos-complement representation [Usage]</li> <li>Explain how fixed-length number representations affect accuracy and precision [Usage]</li> <li>Describe the internal representation of non-numericated data, such as characters, strings, records, and array [Usage]</li> <li>Convert numerical data from one format to another [Usage]</li> </ul> |

| <b>Readings:</b> D. Harris and S. Harris (2012), Patt J.Ashenden (2007), Hennessy and Patterson (2006), Parha                                                                                                                                                                                                                 | and Patel (2005), Patterson and Hennessy (2004),                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Competences:                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Content                                                                                                                                                                                                                                                       | Generales Goals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| <ul> <li>Implementation of simple datapaths, including instruction pipelining, hazard detection and resolution</li> <li>Control unit: microprogrammed</li> <li>Instruction pipelining</li> <li>Introduction to instruction-level parallelism (ILP)</li> </ul> | <ul> <li>Compare alternative implementation of datapath [Assessment]</li> <li>Discuss the concept of control points and the generation of control signals using hardwired or microprogrammed implementations [Familiarity]</li> <li>Explain basic instruction level parallelism usin pipelining and the major hazards that may occur [Usage]</li> <li>Design and implement a complete processor, including datapath and control [Usage]</li> <li>Determine, for a given processor and memory system implementation, the average cycles per instruction [Assessment]</li> </ul> |  |

J.Ashenden (2007), Hennessy and Patterson (2006), Parhami (2005), Stalings (2010), P.Chu (2006)

UNIT 5: Memory system organization and architecture (8)

Competences:

| ontent                                                                                                                       | Generales Goals                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul><li>Storage systems and their technology</li><li>Memory hierarchy: importance of temporal and spatial locality</li></ul> | • Identify the main types of memory technology (e<br>SRAM, DRAM, Flash, magnetic disk) and their re-<br>ative cost and performance [Familiarity] |

| • Main memory organization and operations                                                                                    | • Explain the effect of memory latency on runnin time [Familiarity]                                                                              |

| • Latency, cycle time, bandwidth, and interleaving                                                                           | • Describe how the use of memory hierarchy (cach                                                                                                 |

| • Cache memories (address mapping, block size, re-<br>placement and store policy)                                            | virtual memory) is used to reduce the effective menory latency [Usage]                                                                           |

| • Multiprocessor cache consistency/Using the memory system for inter-core synchronization/atomic mem-                        | • Describe the principles of memory management [U age]                                                                                           |

| ory operations                                                                                                               | • Explain the workings of a system with virtual men                                                                                              |

| • Virtual memory (page table, TLB)                                                                                           | ory management [Usage]                                                                                                                           |

| • Fault handling and reliability                                                                                             | • Compute Average Memory Access Time under a v<br>riety of cache and memory configurations and mix                                               |

| • Error coding, data compression, and data integrity                                                                         | of instruction and data references [Assessment]                                                                                                  |

J.Ashenden (2007), Hennessy and Patterson (2006), Parhami (2005), Stalings (2010), P.Chu (2006)

| Competences:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Content                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Generales Goals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| <ul> <li>I/O fundamentals: handshaking, buffering, pro-<br/>grammed I/O, interrupt-driven I/O</li> <li>Interrupt structures: vectored and prioritized, inter-<br/>rupt acknowledgment</li> <li>External storage, physical organization, and drives</li> <li>Buses: bus protocols, arbitration, direct-memory ac-<br/>cess (DMA)</li> <li>Introduction to networks: communications networks<br/>as another layer of remote access</li> <li>Multimedia support</li> <li>RAID architectures</li> </ul> | <ul> <li>Explain how interrupts are used to implement I/c control and data transfers [Familiarity]</li> <li>Identify various types of buses in a computer system [Familiarity]</li> <li>Describe data access from a magnetic disk drive [Us age]</li> <li>Compare common network organizations, such a ethernet/bus, ring, switched vs routed [Assessment]</li> <li>Identify the cross-layer interfaces needed for mu timedia access and presentation, from image fetch from remote storage, through transport over a communications network, to staging into local memory and final presentation to a graphical display [Familiarity]</li> <li>Describe the advantages and limitations of RAID a chitectures [Familiarity]</li> </ul> |  |

**Readings:** D. Harris and S. Harris (2012), Patt and Patel (2005), Patterson and Hennessy (2004), J.Ashenden (2007), Hennessy and Patterson (2006), Parhami (2005), Stalings (2010), P.Chu (2006)

| UNIT 7: Multiprocessing and alternative architectures (8)<br>Competences:                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <ul> <li>Power Law</li> <li>Example SIMD and MIMD instruction sets and architectures</li> <li>Interconnection networks (hypercube, shuffle-exchange, mesh, crossbar)</li> <li>Shared multiprocessor memory systems and memory consistency</li> <li>Multiprocessor cache coherence</li> </ul> | <ul> <li>Discuss the concept of parallel processing beyond the classical von Neumann model [Assessment]</li> <li>Describe alternative parallel architectures such as SIMD and MIMD [Familiarity]</li> <li>Explain the concept of interconnection networks and characterize different approaches [Usage]</li> <li>Discuss the special concerns that multiprocessing systems present with respect to memory management and describe how these are addressed [Familiarity]</li> <li>Describe the differences between memory backplane, processor memory interconnect, and remote memory via networks, their implications for access latency and impact on program performance [Assessment]</li> </ul> |

| Readings: D. Harris and S. Harris (2012), Patt                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| J.Ashenden (2007), Hennessy and Patterson (2006), Parha                                                                                                                                                                                                                                      | .mi (2005), Stalings (2010), P.Chu (2006)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Competences:                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Content                                                                                                                                                                                                                                                                                                                                                                 | Generales Goals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| <ul> <li>Superscalar architecture</li> <li>Branch prediction, Speculative execution, Out-of-order execution</li> <li>Prefetching</li> <li>Vector processors and GPUs</li> <li>Hardware support for multithreading</li> <li>Scalability</li> <li>Alternative architectures, such as VLIW/EPIC, and Accelerators and other kinds of Special-Purpose Processors</li> </ul> | <ul> <li>Describe superscalar architectures and their advantages [Familiarity]</li> <li>Explain the concept of branch prediction and its utility [Usage]</li> <li>Characterize the costs and benefits of prefetching [Assessment]</li> <li>Explain speculative execution and identify the conditions that justify it [Assessment]</li> <li>Discuss the performance advantages that multithreading offered in an architecture along with that factors that make it difficult to derive maximum benefits from this approach [Assessment]</li> <li>Describe the relevance of scalability to performance [Assessment]</li> </ul> |  |

| <b>Readings:</b> D. Harris and S. Harris (2012), Patt J.Ashenden (2007), Hennessy and Patterson (2006), Parha                                                                                                                                                                                                                                                           | and Patel (2005), Patterson and Hennessy (2004),                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

- 8. Methodology

- 1. El profesor del curso presentará clases teóricas de los temas señalados en el programa propiciando la intervención de los alumnos.

- 2. El profesor del curso presentará demostraciones para fundamentar clases teóricas.

- 3. El profesor y los alumnos realizarán prácticas

- 4. Los alumnos deberán asistir a clase habiendo leído lo que el profesor va a presentar. De esta manera se facilitará la comprensión y los estudiantes estarán en mejores condiciones de hacer consultas en clase.

#### 9. Assessment

Continuous Assessment 1 : 20 %

Partial Exam : 30%

Continuous Assessment 2 : 20 %

Final exam : 30 %

# References

- Harris, David and Sarah Harris (2012). Digital Design and Computer Architecture. 2nd. Morgan Kaufmann. ISBN: 978-0123944245.

- Hennessy, J. L. and D. A. Patterson (2006). Computer Architecture: A Quantitative Approach. 4th. Morgan Kaufman: San Mateo, CA.

- J.Ashenden, Peter (2007). Digital Design (Verilog): An Embedded Systems Approach Using Verilog. Morgan Kaufmann. ISBN: 978-0123695277.

P.Chu, Pong (2006). RTL Hardware Design Using VHDL. 1st. Wiley-Interscience.

Parhami, Behrooz (2005). Computer Architecture: From Microprocessors to Supercomputers. Oxford Univ. Press: New York. ISBN: ISBN 0-19-515455-X.

Patt, Yale N and Sanjay J Patel (2005). Introduction to Computing Systems. 2nd. McGraw Hill.

- Patterson, D. A. and J. L. Hennessy (2004). Computer Organization and Design: The Hardware/Software Interface. 3rd ed. Morgan Kaufman: San Mateo, CA.

- Stalings, William (2010). Computer Organization and Architecture: Designing for Performance. 8th. Prentice Hall: Upper Saddle River, NJ.